technical note

### **Document information**

| Information | Content                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|-------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Keywords    | GaN, FET                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| Abstract    | In this paper we have concentrated on the Power GaN product and technology robustness, quality, reliability and volume manufacturability based on GaN on Si base material. We report here on the product robustness from applications and parametric point of view and qualification testing results of latest generation 650V GaN FETs qualified in accordance with AEC-Q101 standard. Devices offer rated operating temperature of -55°C to +175°C and this family comes with robust gate with high threshold voltage which provides a high safety margin against gate-source transients. Some of the tests are performed beyond AEC-Q101 requirements |

### 1. Introduction

Most efficient power conversion requires best semiconductor devices as the fundamental building block. Power GaN technology offers best possible efficiency. Proving performance is not in question for those closely following the Power GaN technology for its performance demonstration in different applications. Providing robustness of the products in operation, quality, reliability of the technology and the scalability uptake in manufacturing are yet to prove. Power GaN technology is full of challenges. In RF applications they are already successful but in high current high power applications in high voltage, volume manufacturers need to address these challenges to satisfaction. In this paper we'd like to share product robustness for applications, quality and reliability at high voltage and high temperatures, for the Power GaN technology.

Nexperia Power GaN technology focuses on high power applications like AC/DC, PFC, OBC, DC/ DC and Traction Inverters within 650V-900V for Automotive, Telecom, Server, storage, data centres and industrial market sectors

WBG materials with higher critical electric field and higher mobility together give lowest R<sub>DSon</sub> (source drain on state resistance) for higher voltages and significantly better switching FOM (Figure of Merit). WBG devices as beginning to enter the market shows significant promise and takes away many limitations naturally imposed by Si IGBT and Si SJ devices. Some of the hard switched application topologies where Si SJ FETs cannot be used due to the diode reverse recovery can easily use Power GaN FETs and take full advantage of reduced components count and higher efficiency with simpler control schemes.

GaN HEMT (High Electron Mobility Transistor) works with the formation of 2DEG (2 Dimensional Electron Gas) due to the spontaneous polarisation and piezoelectric polarisation combined at the interface of GaN and  $Al_xGa_{1-x}N$ . Epi is formed on Si substrate via seed layer and a graded layer of GaN and AlGaN layers before the pure GaN layer is grown and thin layer of AlGaN then forms the 2DEG. Electron mobility in this layer is very high hence the name.

Current Power GaN FETs are of two main flavour: E-mode or single die normally off device, and D-mode or two die normally off device. Stability and leakage current of the E-mode gates are of concern but two die normally off or cascode configuration currently gives peace of mind as the driving of these FETs are simple and robust. E-mode device drive is complex, especially for high voltage high power applications. For high voltage and high power applications, to avoid gate bounce and harmful shoot through situation, need to have high gate threshold voltage and stable gate drive without worrying for over drive. This is currently not achievable with existing E-mode technologies. The device in our presentation is two die normally off configuration

### 2. Product robustness

The product parameters shared here came from our 50 m $\Omega$  (typical at 25°C) 650 V device but all our products/technology share the same common robustness. Product robustness include parametric assurance like, high reliability gate structure (± 20 V) and high threshold voltage (V<sub>th</sub> = 4 V) that provides a high safety margin against gate source transients induced due to the high drain source dv/dt, high voltage source-drain transient specification (800 V for 650 V device) capable of handling switching transients up to 800 V reliably, rated operating range of -55 °C to 175 °C with T<sub>j(max)</sub> of 175 °C, body diode characteristics with very low V<sub>F</sub> (1.3V @ 12 A) enabling Si-like freewheeling current capability without complex dead time adjustments and along with other parametric performances are part of the product robustness of the GaN product family.

## 3. Quality / qualification of power GaN technology including failure modes

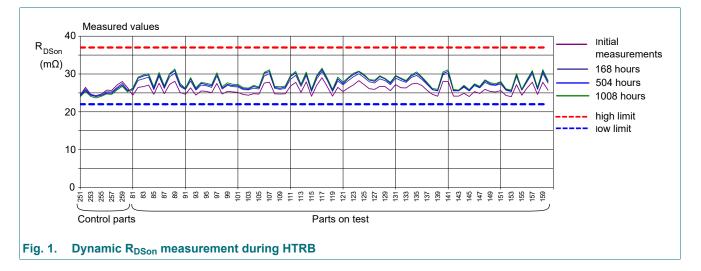

The latest generation 650 V GaN FETs are qualified in accordance with AEC-Q101 Rev D level qualification tests. Results shared here are done on 50 m $\Omega$  (typical at 25 °C) 650 V device that include 650 V, 175 °C High Temperature Reverse Bias (HTRB) tests (1000 hrs) and dynamic R<sub>DSon</sub> shifts. In the following, the term *dynamic* R<sub>DSon</sub> will be used to emphasize that R<sub>DSon</sub> measurements are made with a dynamic, switch-mode test. Temperature cycling tests (1000 cycles) are performed over the range of -55°C to 150°C. High temperature (175 °C) Gate positive (+20 V) and negative (-20 V) bias tests were performed. Further life tests include high temperature biased and unbiased humidity tests and operating life tests. These are only some of the critical tests performed and passed to show the reliability and high quality of the technology.

### 3.1. HTRB

High-Temperature Reverse Bias has been performed at full rated voltage and maximum operating temperature: 650 V and 175 °C. The condition for passing is that  $R_{DSon}$  does not shift by more than 20%. For GaN FETs it is important that  $R_{DSon}$  be tested dynamically to detect any short-term change due to charge trapping. Figure 1 shows the shift in dynamic  $R_{DSon}$  for the test population. Note that the maximum shift is less than 15%. An additional HTRB test was performed and passed at 800 V for 10 hours. This voltage is well above the DC rating, but does correspond to the repetitive transient voltage rating.

### 3.2. HTOL

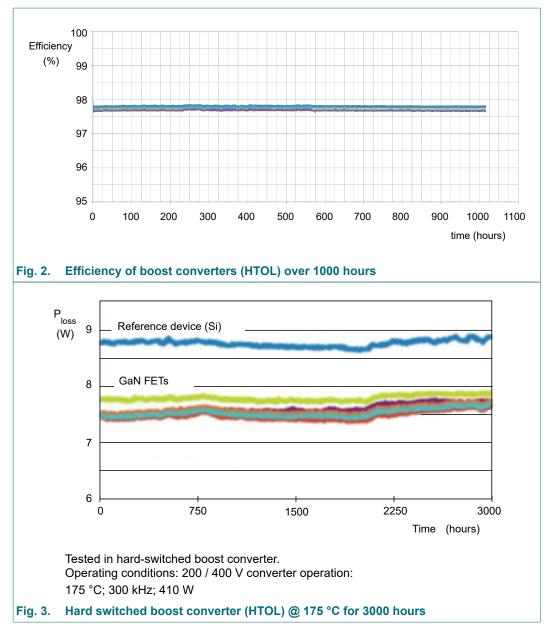

High-Temperature Operating Life tests are not part of the AEC-Q101 standard, but are useful in validating reliability of the parts under actual operating conditions. This is particularly important for new materials, like GaN, to ensure that any new or unfamiliar failure modes are uncovered. A basic half-bridge operating in continuous conduction mode provides the most fundamental exercise of switching behaviour. For this test, a number of identical half-bridge circuits were prepared using two each of the GAN063-650WSA. These were operated continuously as synchronous-boost converters with the following conditions:

- V<sub>in</sub> = 200 V

- V<sub>out</sub> = 480 V

- P<sub>out</sub> = 800 W

- T<sub>i</sub> = 175 °C

- Frequency = 300 kHz

The following graph shows efficiency of all samples during the 1,000 hour test. As may be seen, there is no indication of degradation in any of the sample circuits. Following the tests, all devices were tested for shifts in dynamic  $R_{DSon}$ , leakage current, and threshold voltage. All parameters were found to be stable, with any parametric shift within allowed levels.

## **TN90004**

### An insight into Nexperia Power GaN technology – Applications, quality, reliability and scalability

Failure modes addressed by life testing power GaN technology failure modes can be linked back to the life testing and extra testing performed. Like power cycling relates to wire bond heel crack, temperature cycling address the solder degradation, HTGB look at the gate insulator failure, HTRB addresses the field plate insulator failure while high temperature direct current test addresses the trapped charge in gate region and consequently higher R<sub>DSon</sub> (>20% assumes fail).

## 4. Conclusion

Power GaN technology, though at the early stage of technology maturity offers significant commercial viability with robustness and reliability. For scaling up, tremendous growth potential is better addressed with power GaN technology on Si.

## 5. References

- **1. 600 V JEDEC-qualified highly reliable GaN HEMTs on Si substrates** T. Kikkawa et al., 2014 IEEE International Electron Devices Meeting, San Francisco, CA, 2014, pp. 2.6.1-2.6.4.

- 650 V Highly Reliable GaN HEMTs on Si substrates over multiple generations: matching Silicon CMOS manufacturing metrics and process control — S. Chowdhury, et al., Compound Semiconductor Integrated Circuit Symposium (CSICS), IEEE, 2016.

## 6. Revision history

| Table 1. Revision history |            |                 |  |  |

|---------------------------|------------|-----------------|--|--|

| Revision<br>number        | Date       | Description     |  |  |

| 1.0                       | 2020-07-21 | Initial version |  |  |

# 7. Legal information

#### Definitions

**Draft** — The document is a draft version only. The content is still under internal review and subject to formal approval, which may result in modifications or additions. Nexperia does not give any representations or warranties as to the accuracy or completeness of information included herein and shall have no liability for the consequences of use of such information.

#### Disclaimers

Limited warranty and liability — Information in this document is believed to be accurate and reliable. However, Nexperia does not give any representations or warranties, expressed or implied, as to the accuracy or completeness of such information and shall have no liability for the consequences of use of such information. Nexperia takes no responsibility for the content in this document if provided by an information source outside of Nexperia.

In no event shall Nexperia be liable for any indirect, incidental, punitive, special or consequential damages (including - without limitation - lost profits, lost savings, business interruption, costs related to the removal or replacement of any products or rework charges) whether or not such damages are based on tort (including negligence), warranty, breach of contract or any other legal theory.

Notwithstanding any damages that customer might incur for any reason whatsoever, Nexperia's aggregate and cumulative liability towards customer for the products described herein shall be limited in accordance with the Terms and conditions of commercial sale of Nexperia.

Right to make changes — Nexperia reserves the right to make changes to information published in this document, including without limitation specifications and product descriptions, at any time and without notice. This document supersedes and replaces all information supplied prior to the publication hereof.

Suitability for use — Nexperia products are not designed, authorized or warranted to be suitable for use in life support, life-critical or safety-critical systems or equipment, nor in applications where failure or malfunction of an Nexperia product can reasonably be expected to result in personal injury, death or severe property or environmental damage. Nexperia and its suppliers accept no liability for inclusion and/or use of Nexperia products in such equipment or applications and therefore such inclusion and/or use is at the customer's own risk.

**Applications** — Applications that are described herein for any of these products are for illustrative purposes only. Nexperia makes no representation or warranty that such applications will be suitable for the specified use without further testing or modification.

Customers are responsible for the design and operation of their applications and products using Nexperia products, and Nexperia accepts no liability for any assistance with applications or customer product design. It is customer's sole responsibility to determine whether the Nexperia product is suitable and fit for the customer's applications and products planned, as well as for the planned application and use of customer's third party customer(s). Customers should provide appropriate design and operating safeguards to minimize the risks associated with their applications and products.

Nexperia does not accept any liability related to any default, damage, costs or problem which is based on any weakness or default in the customer's applications or products, or the application or use by customer's third party customer(s). Customer is responsible for doing all necessary testing for the customer's applications and products using Nexperia products in order to avoid a default of the applications and the products or of the application or use by customer's third party customer's third party customer's hird party customer's. Nexperia does not accept any liability in this respect.

**Export control** — This document as well as the item(s) described herein may be subject to export control regulations. Export might require a prior authorization from competent authorities.

**Translations** — A non-English (translated) version of a document is for reference only. The English version shall prevail in case of any discrepancy between the translated and English versions.

#### Trademarks

Notice: All referenced brands, product names, service names and trademarks are the property of their respective owners.

# **List of Tables**

# **List of Figures**

| Fig. 1. Dynamic RDSon measurement during HTRB3                          |

|-------------------------------------------------------------------------|

| Fig. 2. Efficiency of boost converters (HTOL) over 1000 hours           |

| Fig. 3. Hard switched boost converter (HTOL) @ 175<br>°C for 3000 hours |

# Contents

| 1. Introduction                                                               | 2 |

|-------------------------------------------------------------------------------|---|

| 2. Product robustness                                                         | 2 |

| 3. Quality / qualification of power GaN technology<br>including failure modes | 2 |

| 3.1. HTRB                                                                     | 3 |

| 3.2. HTOL                                                                     | 3 |

| 4. Conclusion                                                                 | 4 |

| 5. References                                                                 | 5 |

| 6. Revision history                                                           | 5 |

| 7. Legal information                                                          | 6 |

#### © Nexperia B.V. 2020. All rights reserved

For more information, please visit: http://www.nexperia.com For sales office addresses, please send an email to: salesaddresses@nexperia.com Date of release: 21 July 2020