# DODE APPLICATION HANDBOOK FUNDAMENTALS, CHARACTERISTICS, **APPLICATIONS** Design Engineer's Guide

nexperia

# **Diode Application Handbook**

Fundamentals, Characteristics, Applications

Design Engineer's Guide

### **Contributors**

Reza Behtash

Sebastian Fahlbusch

Surabhi Hiremath

Sebastian Klötzer

Srikanth Yedehalli Lakshmeesha

Burkhard Laue

Nima Lotfi

Martin Röver

Guido Söhrn

Burkhard Stasik

Olaf Vogt

Diode Application Handbook Fundamentals, Characteristics, Applications Design Engineer's Guide

Copyright © Nexperia UK (Ltd) May 2022

#### www.nexperia.com

ISBN 978-0-9934854-9-7

All rights reserved.

No part of this publication may be reproduced or distributed in any form or by any means without the prior written permission of the author.

| Introduction                     |

|----------------------------------|

| Diode fundamentals               |

| Data sheet parameters            |

| Thermal considerations           |

| Diode packaging                  |

| Reliability aspects              |

| Diode applications and use cases |

| Summary                          |

| Αb |  |  |  |

|----|--|--|--|

|    |  |  |  |

|    |  |  |  |

#### **Legal information**

#### **Preface**

Welcome to the Nexperia *Diode Applications Handbook*. Like all of our other Design Engineer's Guides, the Diode Handbook is intended to be a practical, comprehensive and up-to-date reference work written by engineers for engineers, sharing expertise, application insights and best practice to help designers optimize their electronic circuits.

Nexperia and diodes share a common history dating back for the whole of the commercialisation of electronics. Diodes were – of course – one of the fundamental electronic components, first developed over 100 years ago. Similarly, Nexperia can trace its history back over 100 years with names like Mullard, Philips, Valvo, Signetics and NXP ringing through its lineage. Today, Nexperia's extensive portfolio includes diodes, bipolar transistors, ESD protection devices, MOSFETs, GaN FETs and analog & logic ICs, totaling more than 15.000 parts. Virtually every electronic design in the world uses Nexperia components, and these products are recognized as benchmarks in efficiency – in process, size, power and performance. 250 million parts are shipped every single day.

Despite being first developed in the early years of last century, diodes continue to play a vital part in electronic circuits. But, of course they have evolved beyond all recognition from the days of pioneers like Walter Schottky. Most recently, of course we have seen new materials such as silicon carbide emerge which are enabling the realization environmentally-responsible electric vehicles with the performance and range demanded by customers.

The goal of this new handbook – or to give it its full name – *Diode Application Handbook* – *Fundamentals, Characteristics, Applications: Design Engineer's Guide* is to be recognized as the technical dictionary for semiconductor diodes, sharing technical and application insights between the engineering community. Therefore, we proudly invite you to study our Diode Application Handbook – the table of contents will make it easy to navigate.

Finally, I would like to thank Dr.-Ing. Reza Behtash, who has significantly contributed to this edition.

#### Olaf Vogt

Director Product Application Engineering Nexperia

#### **Diode Application Handbook**

## **Table of Contents**

| Chapter<br>Introdu        | 1<br>uction                                             | 16 |

|---------------------------|---------------------------------------------------------|----|

| Chapter<br><b>Diode f</b> | r 2<br>Fundamentals                                     |    |

| 2.1                       | Different types of diodes                               | 20 |

| 2.2                       | Structure and functional principle                      | 22 |

| 2.2.1                     | Recovery rectifiers (P(I)N diodes)                      | 22 |

| 2.2.2                     | Planar Schottky diode                                   | 23 |

| 2.2.3                     | Trench Schottky diode                                   | 24 |

| 2.2.4                     | Silicon germanium (SiGe) diode                          | 27 |

| 2.3                       | Static behavior                                         | 29 |

| 2.4                       | Dynamic behavior                                        | 34 |

| 2.4.1                     | Forward recovery                                        | 34 |

| 2.4.2                     | Reverse recovery                                        | 35 |

| 2.5                       | Benchmarking of different technologies                  |    |

|                           | in terms of switching                                   | 37 |

| 2.5.1                     | Evaluation parameters                                   | 37 |

| 2.5.2                     | Sample selection                                        | 38 |

| 2.5.3                     | Impact of the temperature on the switching performance  | 39 |

| 2.5.4                     | Why is the Trench Schottky diode superior               |    |

|                           | in terms of switching                                   | 41 |

| 2.5.5                     | Impact of the slope gradient on switching performance   | 44 |

| 2.5.6                     | Impact of the turn-off current on switching performance | 45 |

| 2.5.7                     | Impact of the reverse voltage on switching performance  | 46 |

| 2.6                       | SiC rectifier                                           | 48 |

| 2.6.1                     | Introduction                                            | 48 |

| 2.6.2                     | Material properties of 4H-SiC                           | 49 |

| 2.6.3                     | SiC enabling superior power diodes and                  |    |

|                           | changing the high voltage diode landscape               | 50 |

| 2.6.4                     | Advanced SiC MPS process for maximum performance        | 62 |

| 2.7                       | Zener diodes                                            | 64 |

| 2.7.1                     | Introduction                                            | 64 |

| 2.7.2                     | Datasheet parameters                                    | 65 |

| 2.7.3                     | Zener diodes package overview                           | 66 |

#### Chapter 3

|   |     | -  |     |    |    |    |   |    |   |    |

|---|-----|----|-----|----|----|----|---|----|---|----|

|   |     |    |     |    |    |    | - |    | - |    |

| u | ata | SI | ıee | C. | υa | Iа | m | eu | е | 15 |

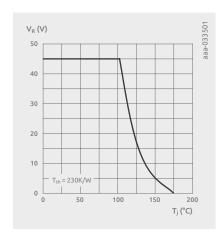

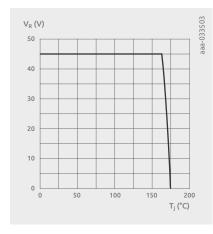

| 3.1<br>3.2<br>3.2.1<br>3.2.2<br>3.2.3<br>3.2.4<br>3.2.5<br>3.2.6 | Introduction Understanding Nexperia datasheet parameters and where they can be found. Quick reference data Pinning-, ordering- and marking information Limiting values Thermal characteristics Electrical characteristics. Datasheet temperature curves | 78<br>78<br>78<br>81<br>81<br>85<br>88<br>93 |

|------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------|

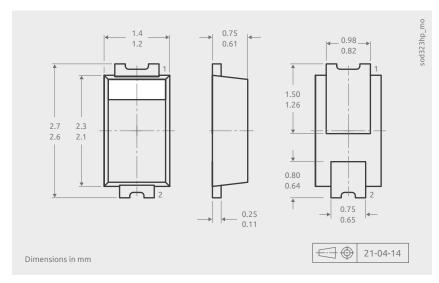

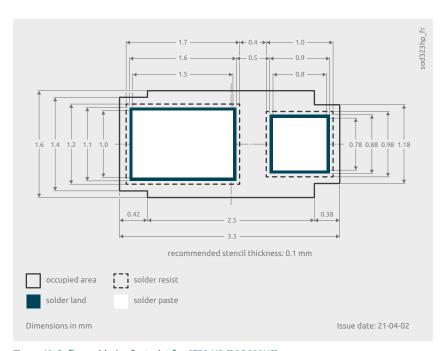

| 3.2.7                                                            | Package outline & recommended footprint for reflow soldering                                                                                                                                                                                            | 96                                           |

| Chapter 4 Thermal                                                | 4<br>considerations                                                                                                                                                                                                                                     |                                              |

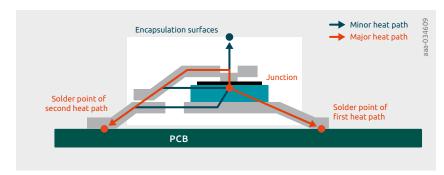

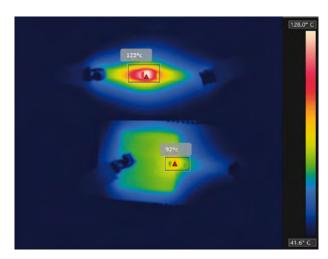

| 4.1                                                              | Diode as a thermal system                                                                                                                                                                                                                               | 100                                          |

| 4.1.1                                                            | Measurement of thermal resistances                                                                                                                                                                                                                      | 101                                          |

| 4.1.2                                                            | Definition of thermal resistances                                                                                                                                                                                                                       | 102                                          |

| 4.1.3                                                            | Approximations                                                                                                                                                                                                                                          | 104                                          |

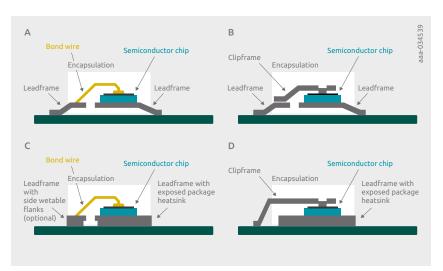

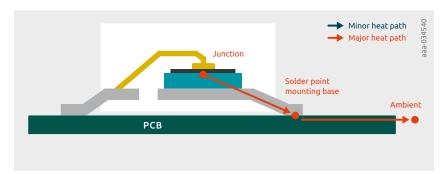

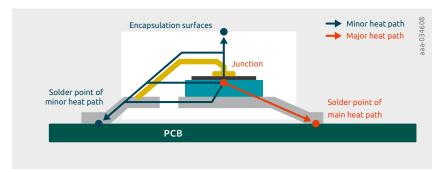

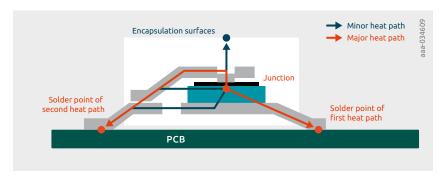

| 4.1.4                                                            | Clip bonded packages                                                                                                                                                                                                                                    | 105                                          |

| 4.1.5                                                            | Multiple chip devices                                                                                                                                                                                                                                   |                                              |

| 4.1.6                                                            | R <sub>th(j-c)</sub> and why we call it Ψ(j-top)                                                                                                                                                                                                        |                                              |

| 4.2                                                              | Thermal considerations in forward bias                                                                                                                                                                                                                  |                                              |

| 4.2.1                                                            | Continuous current                                                                                                                                                                                                                                      |                                              |

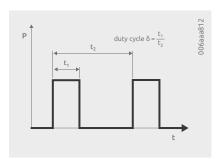

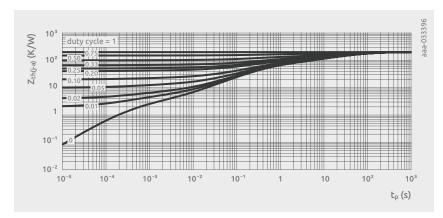

| 4.2.2                                                            | Pulsed operation                                                                                                                                                                                                                                        | 109                                          |

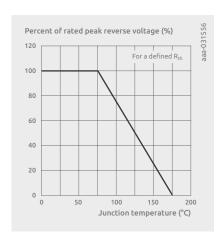

| 4.3                                                              | Thermal considerations in reverse bias                                                                                                                                                                                                                  |                                              |

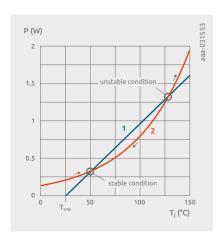

| 4.3.1                                                            | Rectifier as thermal system – thermal runaway                                                                                                                                                                                                           | 111                                          |

| 4.3.2                                                            | The safe operating area (SOA) of a rectifier                                                                                                                                                                                                            |                                              |

|                                                                  | in reverse direction                                                                                                                                                                                                                                    | 114                                          |

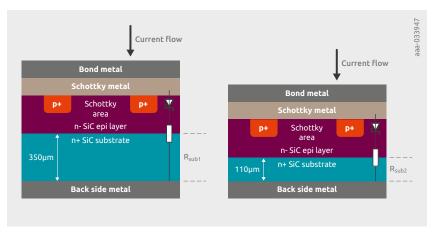

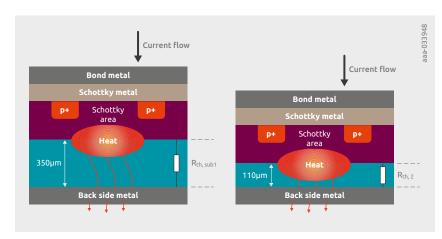

| 4.3.3                                                            | Impact of technology on the SOA of a rectifier                                                                                                                                                                                                          |                                              |

| 4.3.4                                                            | Impact of package on the SOA of a rectifier                                                                                                                                                                                                             |                                              |

| 4.4                                                              | Transient effects                                                                                                                                                                                                                                       |                                              |

| 4.4.1                                                            | The dynamic thermal impedance Z <sub>th</sub>                                                                                                                                                                                                           |                                              |

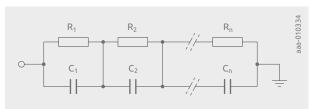

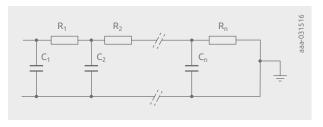

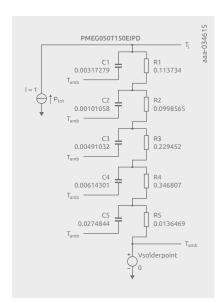

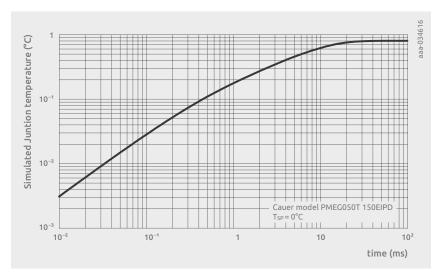

| 4.4.2                                                            | Foster and Cauer model.                                                                                                                                                                                                                                 |                                              |

|                                                                  |                                                                                                                                                                                                                                                         |                                              |

#### Chapter 5

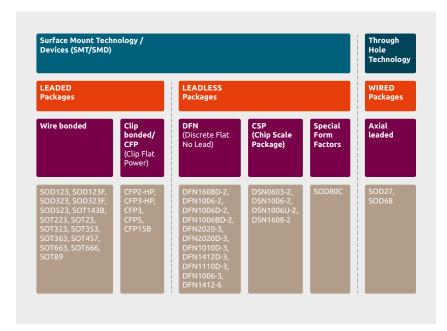

#### Diode packaging

| 5.1       | Through-hole packages                                 |     |

|-----------|-------------------------------------------------------|-----|

| 5.2       | Packages for surface-mounted devices                  | 131 |

| 5.2.1     | Wire-bonded leaded packages                           | 132 |

| 5.2.2     | Clip Flat Power (CFP) packages                        | 133 |

| 5.3       | Leadless packages                                     | 134 |

| 5.3.1     | Leadframe-based Dual-Flat-No-Leads packages (DFN)     | 134 |

| 5.3.2     | Chip Scale Packages (CSP)                             | 135 |

| 5.4       | Soldering techniques                                  | 136 |

| 5.4.1     | Wave soldering                                        | 136 |

| 5.4.2     | Reflow soldering                                      | 136 |

| Chapter 6 |                                                       |     |

|           | y aspects                                             |     |

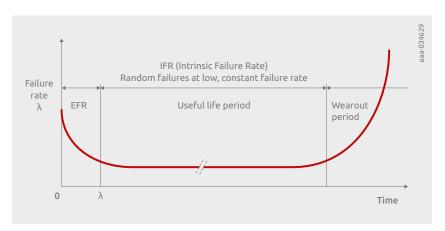

| 6.1       | Probability of failure                                | 141 |

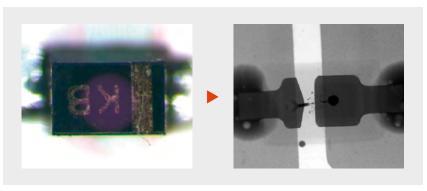

| 6.2       | Reliability tests & failure modes                     |     |

| 6.3       | Automotive-grade qualification                        |     |

| 6.4       | Mission profiles                                      | 146 |

| 6.5       | Nexperia's high robustness specification              | 147 |

| Chapter 7 | ,                                                     |     |

|           | plications and use cases                              |     |

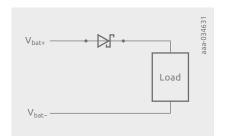

| 7.1       | Polarity protection diode                             | 150 |

| 7.2       | Zener applications                                    |     |

| 7.3       | ORing applications                                    | 159 |

| 7.4       | Switching diode                                       | 160 |

| 7.5       | Bootstrap diode                                       | 165 |

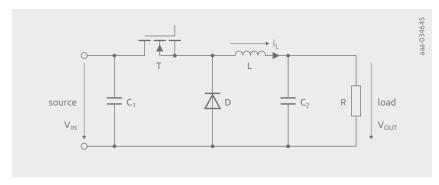

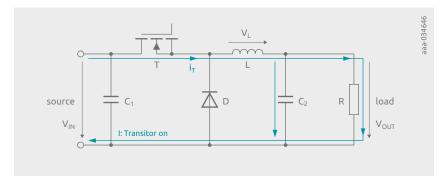

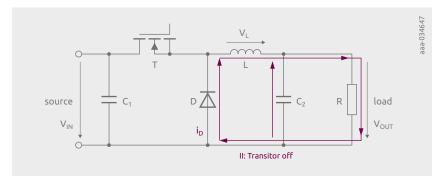

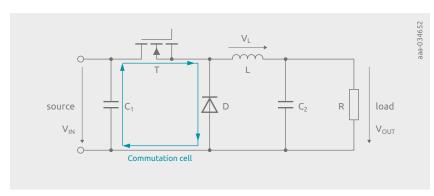

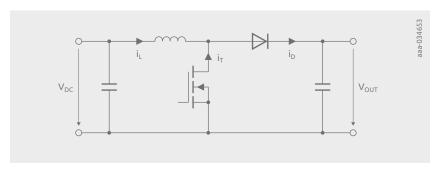

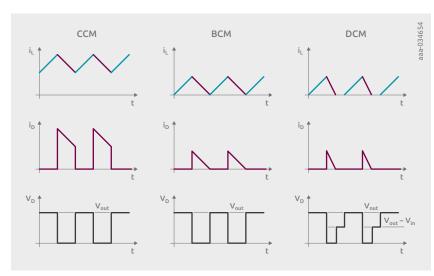

| 7.6       | Overview of hard-switching DC-DC converter topologies | 170 |

| 7.6.1     | Principles of hard-switching topologies               | 170 |

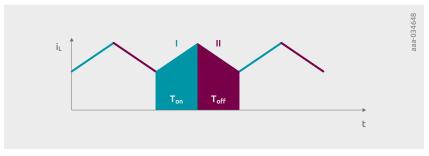

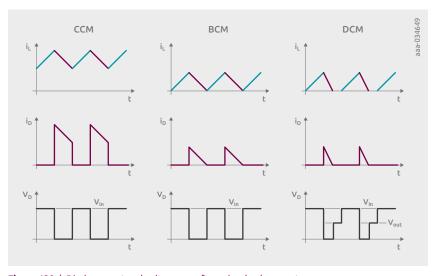

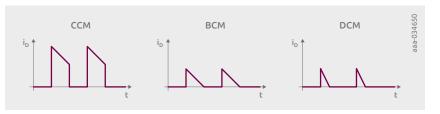

| 7.6.2     | Diode power losses in CCM, BCM and DCM                | 174 |

| 7.7       | Topologies                                            | 182 |

| 7.7.1     | Buck converter                                        | 182 |

| 7.7.2     | Boost converter                                       | 183 |

| 7.7.3     | Buck-boost converter                                  | 184 |

| 7.7.4     | Flyback converter                                     | 186 |

#

# Chapter 1 Introduction

Introduction

The history of semiconductor diodes underpins the entire history of electronics. and while it is easy to overlook diodes, today they have never been more relevant or diverse. Nexperia's diode expertise stretches back to the 1950s and the Valvo/ Philips Semiconductors facilities in Hamburg, Germany. In the intervening 70 years the company has built a very broad portfolio of devices including Small Signal Switching and Zener Diodes, very efficient Schottky Diodes and Power Rectifiers in modern Trench technologies.

Highlighting a few important milestones:

The development of special diodes with variable junction capacity, so called "Vericap" diodes, begins in 1964.

In the 1970s the production of Glass Diodes in the famous SOD68 commences. Nexperia is still known as the packaging innovator – the famous SOT23 3-pin package, invented in 1969, is still the world's largest-selling semiconductor package. In the 1980s and 1990s the number of 'leaded SMD' massively increased due to high-volume consumer products like PCs, Laptops, TVs etc. In the early 2000 diodes in leadless packages were introduced, supporting the needs of the recordbreaking Mobile / Smart Phone Industry. Latest packaging considerations are discussed in Chapter 5 of this handbook.

The first decade of the 21st century was also when Nexperia built its successful ESD Diode product portfolio (readers are advised to read the ESD Application Handbook and the ESD Automotive Edition.)

Developments continue apace and in this current decade, there have been, perhaps for some, surprising introductions. How familiar, for example, are most readers with new silicon germanium products (the first SiGe rectifiers were brought to market in 2020 by Nexperia)? Another case in point is silicon carbide. A visit to a trade show or quick web search will confirm that SiC outperforms silicon devices in certain applications. But what are the material properties that deliver this performance boost and how can designers benefit most from new SiC rectifiers? This book will tell you.

The content of the Diode Application Handbook will benefit readers by sharing a wealth of technical information, from basic fundamentals up to design ideas.

Chapter 2 explains the fundamentals, looking at diode types and behavior. Chapter 3 looks at the parameters commonly listed in diode datasheets, and how to interpret that information. Chapter 4 is devoted to thermal considerations, and Chapter 5 focuses on one of Nexperia's key strengths: packaging innovation, which is so influential on reliability and performance. Chapter 6 concerns itself with reliability, including Automotive-grade qualification. The application's chapter (7) at the end of the handbook highlights several basic functions (including polarity

protection and freewheeling functionality for inductive loads) that diodes provide in electronic systems. These sub-circuit insights help to address real-world challenges in electronic design.

Earlier, we mentioned electric vehicles as one obvious example of an application where new diode technologies are playing a vital, enabling role: in reality, very few electronic systems exist without some form of diode performing a vital function. Diodes are used in data centers, 5G, robotics, IoT systems, 'smart' installations – home/office/factory/city – medical equipment, in consumer electronics like mobile phones and in high-reliability mission-critical space expiration.

Efficiency is the mantra of our times, either for reasons of size, power consumption, performance or cost, or perhaps all four. Correct component selection will optimize the final design; poor choices will lead to compromise. As one of the most fundamental electronics building blocks, the diode is – as readers will see – not merely the humble discrete component that can be considered at the last minute.

The Diode Applications Handbook will satisfy engineers who wish to get more insights on fundamentals and applications insights. The focus on engineering aspects and technical challenges provides vital background information that will enable the engineer to optimize designs to ensure best product performance. But the book never falls into the trap of becoming a mere academic exercise. Its pages detail practical solutions to real world problems with applicable circuits and formulas. Chapter 7, Diode applications and use cases, is particularly strong here with sections on polarity protection, ORing, hard switching, power supply design and more.

This reference work represents the collected knowledge of some of our industry's most respected experts. But these are people who deal on a daily basis with questions from engineers. They know what questions are commonly asked and they are delighted to be able to share their research and experience widely and freely. We hope that you find this work informative and useful.

Nexperia continually updates product information and application notes. Please visit our Nexperia Encyclopaedia handbook series www.nexperia.com/design-engineers-guides to read our other handbooks:

- MOSFET & GaN FET Application Handbook

- LOGIC Application Handbook

- ESD Application Handbook and

- ESD Application Handbook: Automotive Edition

# Chapter 2 **Diode fundamentals**

# 2.1 Different types of diodes

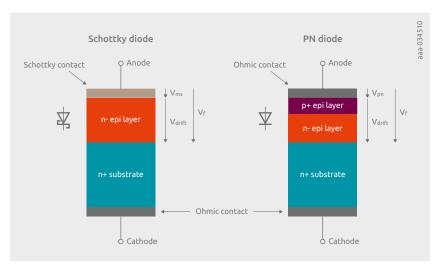

Figure 1 | Sketch showing the layer structure of Schottky (left) and PN diodes.

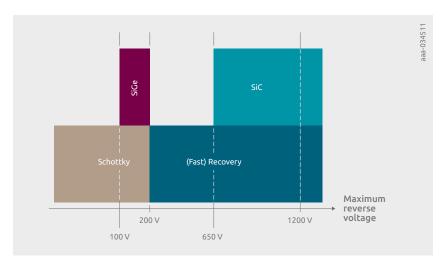

**Figure 2** | Overview of different technologies for discrete diodes depending of max. reverse voltage.

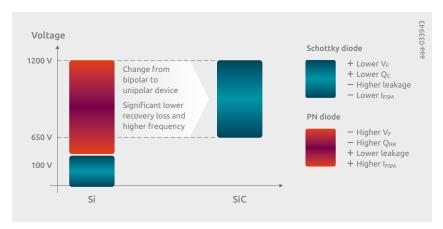

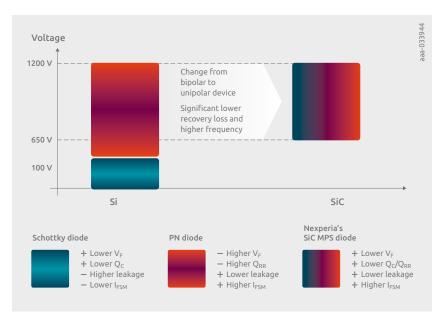

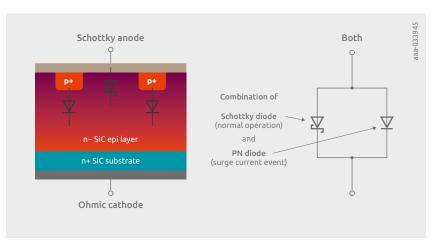

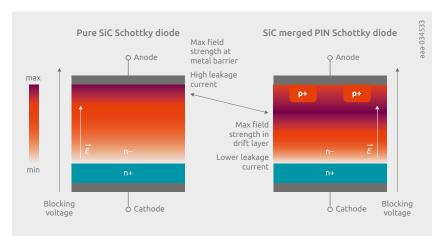

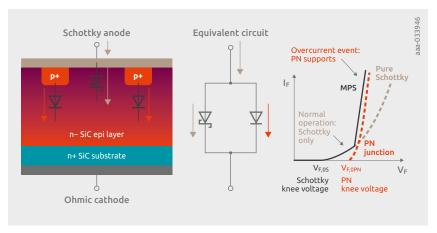

An ideal diode will generally have a low forward voltage drop, a high reverse blocking voltage, zero leakage current and a low parasitic capacitance, facilitating a high switching speed. When considering the forward voltage drop, there are two main elements contributing to the overall voltage drop  $V_F$ , as shown in Figure 1: the voltage drop across the junction – a p-n junction in case of recovery rectifiers and Zener diodes and a metal-semiconductor junction in case of Schottky rectifiers; and the voltage drop across the drift region. The forward voltage drop across the p-n junction is intrinsically determined by the built-in voltage and hence, mainly by the chosen semiconductor and its doping. On the other hand, the forward voltage drop across the metal-semiconductor interface in a Schottky barrier rectifier can be modified by the choice of the Schottky metal, with the Schottky barrier being the result of the difference between the metal work function and the electron affinity of the semiconductor. By using Schottky metals with a low metal work function, the voltage drop across the metal semiconductor interface can be minimized. However. there is a trade-off between the forward voltage drop across the junction and the leakage current of the Schottky rectifier, as the level of the leakage current is also determined by the Schottky barrier and the electrical field across the metal semiconductor interface. In addition to this trade-off, the advantage of a low voltage drop across the junction can disappear when the thickness of the drift region is increased in order to achieve a high reverse blocking voltage. This is the reason why the reverse blocking voltage of Schottky rectifiers is traditionally limited to well below 200V. These considerations lead to the overview of utilized technologies for discrete diodes based on maximum reverse voltage, as shown in Figure 2. As already mentioned, Schottky diodes are normally used up to a maximum reverse voltage of approx. 200V; beyond 200V, Schottky diodes lose their intrinsic advantage. After this point, recovery rectifiers are used. A distinction is made for recovery rectifiers between different switching speeds. This classification will be described in the chapter on dynamic behavior (2.4). The operating range of a silicon carbide (SiC) diode starts at 650V. Thanks to the wide bandgap of SiC this range extends to well above 1700V. Figure 2 also shows a new technology called silicon germanium (SiGe). The maximum reverse voltage range of SiGe diodes is between 100 and 200V, at around about the interface between Schottky diodes and recovery rectifiers.

This chapter will discuss the various diode types and technologies regarding their internal structure, static and dynamic behavior.

### 2.2 Structure and functional principle

#### 2.2.1 Recovery rectifiers (P(I)N diodes)

Recovery rectifiers are based on a classical p-n junction in the device structure. An n-doped drift laver is epitaxially grown on the n+ substrate which serves as the cathode of the vertical device. The anode of the diode is realized by implanting and diffusing a p dopant into the epitaxial layer. The p diffusion step determines the profile of the p well, and it is therefore crucial for the breakdown voltage of the diode. The maximum reverse voltage of recovery rectifiers starts at around 200V and increases to approximately 1700V. Diodes at the higher end of the reverse voltage range consist of a p-i-n-junction rather than a p-n interface, as the almost undoped layer between the p and n region allows for a further expansion of the depletion laver while the device is reverse biased. A top metallization laver is used to create an ohmic contact to the anode of the diode.

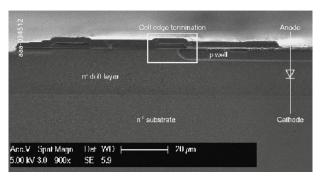

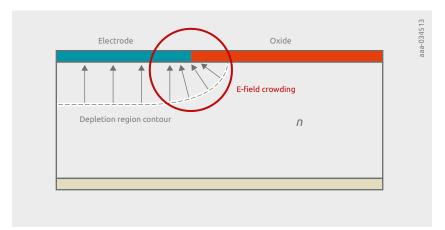

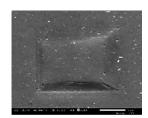

The Scanning Electron Microscope (SEM) image in Figure 3 shows the cross section of a recovery rectifier. In order to highlight the different doping regions, the sample has been treated with a special etchant, making the doping interfaces clearly visible. In this picture one can see very clearly the shape of the p well at the edge of the active region. This shape decides the contour of the depletion region of the p-n junction when the diode is reverse biased, and together with the field plate it forms the termination area for this device. Proper edge termination of the active cell is important in order to avoid the crowding of the electrical field in this area which could lead to premature breakdown and increased leakage current. Figure 4 illustrates a simplified sketch showing the contour of the depletion region and the resulting crowding of the electrical field at the edge of the active cell. As we will see later on, the termination design can also impact the dynamic behavior of the device. The epitaxial layer of recovery rectifiers is often intentionally contaminated with gold or platinum. The Au and Pt atoms in the silicon layers act as traps for the charge carriers and reduce the lifetime of minority carriers. This so-called 'lifetime kill' has a huge impact on the dynamic behavior of the device and will be discussed in section 2.4.

Figure 3 | SEM picture showing the cross section of a recovery rectifier. The sample has been etched in order to decorate the different doping regions.

Figure 4 | The so-called 'E-Field crowding' at the edge of the active cell leads to premature breakdown and increased leakage current. A proper edge termination prevents the increased electrical field concentration at the edge of the active cell.

#### 2.2.2 Planar Schottky diode

The Schottky diode – named after its inventor, the German physicist Walter Hans Schottky – consists essentially of a metal-semiconductor interface. Because of its low forward voltage drop and high switching speed, the Schottky diode is widely used in a variety of applications, such as the boost and buck diode in power conversion circuits. The electrical performance of a Schottky diode is, of course, subject to physical trade-offs, primarily between the forward voltage drop, the leakage current and the reverse blocking voltage. The most important consideration for balancing the trade-off between the forward voltage drop and the leakage current is the chosen Schottky metal. The higher the metal work

doping.

function of the Schottky metal, the higher the barrier height, and therefore the

higher the forward voltage drop and the lower the leakage current of the Schottky

diode (and vice versa). The breakdown voltage of the Schottky diode on the other

hand is primarily determined by the choice of the epitaxial layer thickness and

Figure 5 | SEM picture showing the cross section of a planar Schottky diode. The sample has been etched in order to highlight the different doping regions. The termination consisting of guard ring and field plate is clearly visible.

Figure 5 illustrates the cross section of a planar Schottky diode. The sample has been etched in order to delineate the different doping regions in the device. The etching also highlights the edge termination concept of the planar Schottky diode. The so-called 'guard ring' consists of a p-doped region beneath the oxide opening at the edge of the active area. The guard ring has a huge impact on the leakage current of the Schottky diode as it prevents the electrical field crowding at the edge of the active region, as discussed earlier and shown in Figure 4. But the guard ring is also ultimately a pn junction at the edge of the active area parallel to the actual metal-semiconductor junction. When the diode is forward biased with a high forward voltage – high enough to switch on this pn diode, the guard ring contributes to the forward current of the Schottky diode, enhancing the current capability of the device. But it can also have a detrimental effect on the switching behavior of the Schottky, as will be discussed later in the dynamic behavior section 2.4.

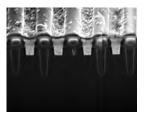

#### 2.2.3 Trench Schottky diode

The widely-known one-dimensional silicon limit describes the general trade-off between the achievable breakdown voltage and the specific on-resistance of a silicon layer sandwiched between two electrodes. One could overcome the 1D silicon limit and decrease the specific on-resistance for a given breakdown voltage by flattening the profile of the electrical field in the semiconductor layer. In an ideal case, the electrical field would be constant along the drift layer rather than having a peak surpassing the critical electrical field in the given semiconductor. There are basically two concepts for flattening the electrical field profile which are used in commercial products: the super junction and the trench. The concept behind the

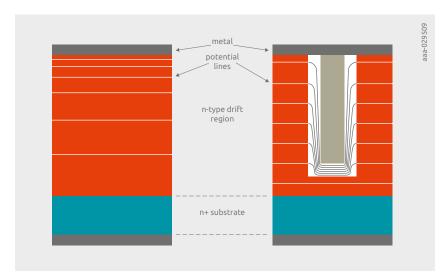

Trench Schottky rectifier is termed 'RESURF' (reduced surface field). The RESURF effect is illustrated in Figure 6. In a planar Schottky rectifier the equipotential lines are concentrated close the top electrode, resulting in a high electrical field near the surface. This results in a strong increase of the leakage current with increasing reverse voltage, and an early breakdown when the critical electrical field is exceeded near the surface.

**Figure 6** | Equipotential lines in a planar Schottky rectifier (left) and in a Trench Schottky rectifier (right) in reverse direction.

The top metal layer represents the anode, the bottom metal layer is the cathode.

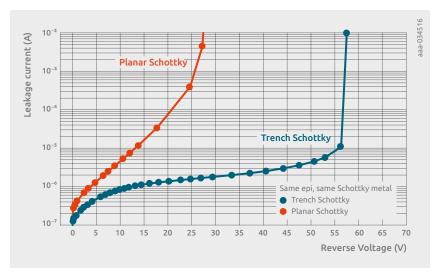

By etching trenches into the silicon and filling them with polysilicon – electrically separated from the drift region by a thin dielectric – the trenches act like a field plate in the semiconductor, depleting the drift region in reverse direction and resulting in a flattened electrical field profile along the drift region. Therefore, the maximum electrical field is occurring inside the dielectric layer at the bottom of the trench rather than at the surface of the epi layer. The trench concept gives the device designer an additional degree of freedom to design and to optimize the device with respect to one of its parameters. Therefore, it is possible to use trenches to reduce the leakage current of the Schottky diode for a given epitaxial layer thickness, doping and Schottky metal. This is illustrated in Figure 7, where the reverse characteristics of a planar Schottky diode is compared to a Trench Schottky diode with the same epitaxial structure (doping and thickness), and the same Schottky metal and die size.

Figure 7 | The reverse characteristics of a planar Schottky vs. a Trench Schottky with the same epitaxial thickness and doping, same Schottky metal and die size.

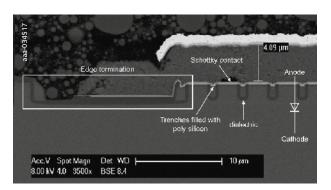

Figure 8 | SEM picture showing the cross section of a trench Schottky diode. The edge termination area is highlighted and consists of a wide trench covered by a field plate. Consequently there is no guard ring and thus no pn junction (as would occur for a planar Schottky).

However, it is also possible to use trench technology to improve the forward voltage drop V<sub>f</sub> of the Schottky diode, by increasing the doping concentration of the epitaxial layer without sacrificing the leakage current level of the device. This can also be useful for a die-shrink to house the diode in a smaller package.

The cross section of a trench Schottky diode is shown in Figure 8. Aside from the trenches, an obvious difference to a planar Schottky design is the termination concept, which consists of a wide trench. A field plate covers this trench to its center. Consequently, there is no guard ring and thus no pn junction in the device, at least for trench Schottky diodes with a maximum reverse voltage of up to approximately 100V. The impact of this termination concept on the switching behavior of the Trench Schottky diode will be discussed in section 2.5.4.

#### 2.2.4 Silicon germanium (SiGe) diode

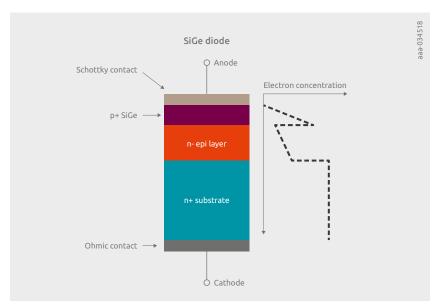

Silicon germanium (SiGe) is a compound semiconductor well known as the base material for hetero-junction bipolar transistors (HBT) since the 1990s. Over the last years, Nexperia has adapted this Technology for use in diodes. At the beginning of 2020 the first SiGe rectifiers were brought to the market by Nexperia.

When considering performance, the SiGe diode can be interpreted as a hybrid technology between Schottky and a recovery rectifier (PN diode). It combines the high efficiency of Schottky rectifiers, in terms of a low forward voltage drop, with the low reverse leakage currents and the thermal stability of PN diodes.

To better comprehend the excellent trade-off between  $V_F$  and  $I_R$  Figure 9 shows the structure of the SiGe diode. The epitaxial layers of the devices are grown on standard n+ silicon substrates. Therefore, conventional tools and processes are used for mass production. On top of the n- drift layer there is a very thin and highly p-doped silicon germanium layer. One obstacle to overcome is the accurate formation of the SiGe interface, as the lattice mismatch between silicon and germanium is greater than 4%. To prevent the interface having misfit dislocations. investigations have shown that reliable junctions may be formed if the germanium content is low and the SiGe layer is thin. [Ashburn, Peter (2003): SiGe Heterojunction Bipolar Transistors, University of Southampton, UK: John Wiley & Sons, Ltd]. The cathode of the diode consists of the back side metallization which forms an ohmic contact, as with other diode types.

The thin SiGe laver leads to a big gradient of the electron concentration, as illustrated in Figure 9. Along with the higher intrinsic carrier concentration of SiGe compared to Si  $(n_{isige}^2 >> n_{isi}^2$  as a result of the smaller band gap), this leads to a significant diffusion component of the current in the structure:  $J = q \times D_n \times \frac{\partial n}{\partial u}$ . This means that for a given forward voltage drop, a higher current density can be achieved with this structure as compared to a pure p-n junction. Equally, if  $V_{\rm f}$  is lower, there is less stored charge in the layer for a given current density. This also results in an improvement in the switching behavior of the SiGe diode as compared to recovery rectifiers, as will be shown in section 2.5.

Figure 9 | Structure of the SiGe diode together with simplified electron concentration along the structure. The very thin and highly p-doped silicon germanium layer together with the higher intrinsic carrier concentration of SiGe (due to its narrower bandgap leading to  $n_i^2_{SiGe} \approx n_i^2_{Si}$  leads to a significant diffusion current in the structure:  $J = q \times D_n \times \frac{\partial n}{\partial x}$ .

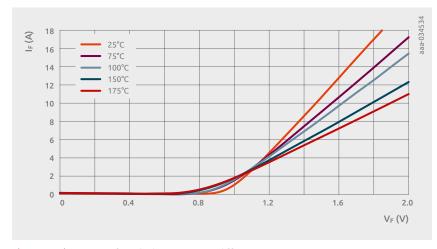

#### 2.3 Static behavior

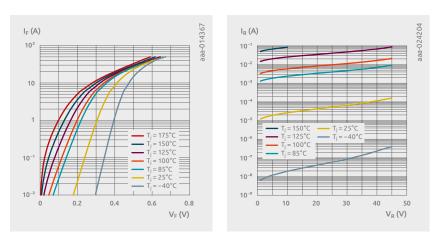

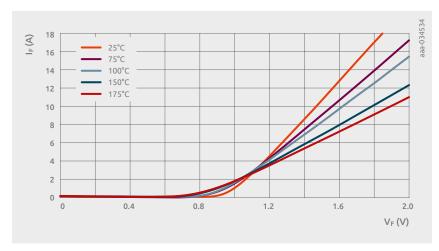

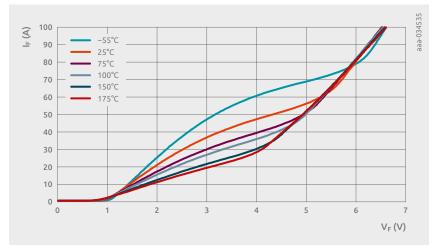

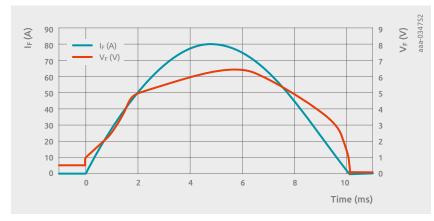

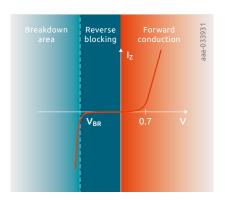

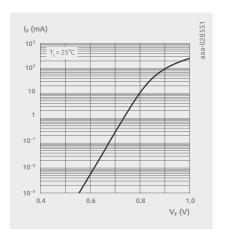

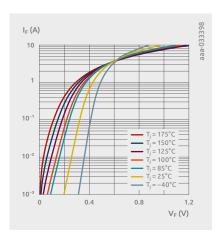

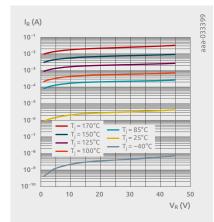

The static behavior of a diode is described by its current/voltage (IV) characteristics in forward and reverse direction in the data sheet. As an example, the IV characteristics of the Schottky diode PMEG045V150EPD are shown in Figure 10. Both the forward characteristics and the reverse characteristics exhibit a strong temperature dependence. The higher the temperature the lower the forward voltage drop, and the higher the leakage current of the diode in reverse direction. This is the case for all diode technologies, whether controlled by a metal semiconductor junction as in the case of Schottky diodes or a pn junction as for recovery rectifiers. In forward direction, the exponential dependence of the forward current on the forward voltage can be seen as a straight line on the logarithmic scale. As a general approximation, a voltage drift of approximately -1.7mV per Kelvin increase can be assumed for the impact of temperature on  $V_{\rm F}$ (and approximately –2mV per Kelvin for recovery rectifiers). At higher currents, the impact of the voltage drop across the epitaxial layer increases and limits the current capability of the device. This leads to the observation that in this region. the curves for almost all temperatures run together. In reverse direction (right picture in Figure 10) there is also an exponential impact of the temperature on the reverse leakage current. Here, too, the exponential temperature dependence is not limited just to Schottky devices; it is also the case for recovery rectifiers. It is also interesting to mention that the different diode technologies share the fact that the breakdown mechanism in these devices is dominated by the avalanche breakdown.

Figure 10 | IV characteristics of PMEG045V150EPD. Left: forward characteristics. right: reverse characteristics. Please note: all points are measured in pulsed mode, excluding any self-heating of the device.

In contrast to tunneling breakdown, the breakdown voltage caused by avalanche effect increases with temperature, as the rate of scattering mechanisms for the electrons increases with temperature, reducing the energy of the charge carriers and thus reducing the avalanche effect.

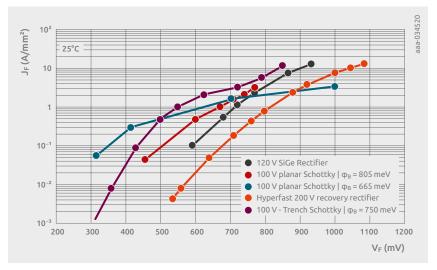

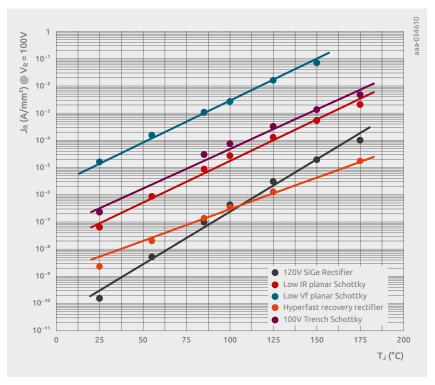

Now let us compare the static behavior of the different described diode technologies. Since the currents of the diodes in forward and reverse direction naturally scale with the size of the die (strictly speaking with the size of the active area), a normalization of the currents with respect to the die size is necessary in order to have a fair comparison of the different technologies. And as the different diode technologies are designed for different voltage ranges, it is also necessary to choose a voltage range that is reasonably suitable for all technologies. For this reason. Figure 11 shows the forward current density for several diode types used in the 100V voltage range. The diode technologies under investigation are: 120V silicon germanium, planar Schottky with a barrier height of 805meV, planar Schottky with a barrier height of 665meV, 200V hyper fast recovery rectifier (hyper fast recovery rectifiers are not available below 200V) and finally 100V Trench Schottky with a barrier height of 750meV. In this graph, the forward current is normalized with respect to the active area of the device. For Trench Schottky devices this means that the currents are normalized with respect to the sum of all mesa areas.

As expected, the forward voltage drop  $V_f$  is the highest for the hyper fast recovery rectifier for a given current density. The reason is obvious: the built-in voltage across the pn junction needs first to be equalized before a significant amount of current starts to flow. Thanks to the bipolar nature of the hyper fast recovery rectifier, these devices show a distinctive current-carrying capability up to high current densities.

The advantage of silicon germanium technology described in 2.2.4 can also be seen in Figure 11 as the SiGe diode exhibits significantly more current density for a given forward voltage compared to the hyperfast recovery rectifier. So, if the die size is limited by a specific type of package (and thus by the maximum die size in this package) it can be advantageous to use a SiGe die instead of a recovery diode in order to get more current out of the given package.

Now let's have a look at the unipolar devices in Figure 11. In a Schottky diode, the forward current is transported via thermionic emission. The majority carriers have to overcome the barrier height in order to transport the current. Therefore, the higher the barrier height the higher the necessary forward voltage for a given current density. This is the reason why the planar Schottky device with a barrier height of 805meV exhibits the highest forward voltage drop amongst the investigated Schottky diodes. The planar Schottky with a barrier height of 665meV has a low forward voltage drop for low current densities, however the curve

flattens out very quickly. This is due to the thick drift layer of this 100V device with such low barrier height, which is necessary to achieve the required breakdown voltage and to control the leakage current in reverse direction. This thick drift layer leads to a significant voltage drop across this layer at higher current densities, limiting the current transport capability of the diode. This is already described in section 2.1 which details why the reverse blocking voltage of Schottky diodes is limited to a voltage range of 150–200V. Otherwise very high barrier heights would be necessary for higher reverse voltages, which, in turn, would increase the forward voltage drop and diminish the current capability.

Figure 11 | Pulsed forward current density (normalized forward current with respect to the active area) for different 100V technologies at room temperature.

Section 2.2.3 describes that, because of the RESUR effect, Trench Schottky devices can have a significantly higher doping level in the drift layer compared to their planar counterparts, without suffering penalties regarding breakdown voltage or leakage current. This can be seen in Figure 11. The Trench Schottky device with a barrier height of 750meV has a higher forward voltage drop for low current densities compared to the planar Schottky with a barrier height of 665meV. However the curve doesn't flatten when the forward voltage is increased – as in case of the planar Schottky. This is due to the higher doping of the drift layer, resulting in significantly less voltage drop across the drift layer. The low-ohmic drift layer reveals yet another phenomena, the so-called 'hole-injection'. There are holes above the Fermi level in the Schottky metal which can be injected from the metal into the semiconductor (equivalent to valence band electrons in the semiconductor acquiring enough thermal energy to leave the silicon and enter into one of the

empty states above Fermi level in the metal, leaving behind a hole in the valence band). The barrier height for these holes entering the semiconductor is not high – just the difference between the band gap energy of silicon and the barrier height for the electrons. This, in turn, means that the hole injection is higher when the metal work function of the chosen Schottky metal is higher ('low leakage' Schottky metals have more hole injection).

In equilibrium or in low forward voltage bias, the injected holes are 'trapped' in a potential well below the valance band. But if the Schottky diode is under strong forward bias, the holes can leave the potential well and contribute to the current in the device. So, surprisingly, the unipolar Schottky diode can also have a bipolar component under strong forward bias, especially for high barrier types. This can be seen in Figure 11 for the Trench Schottky device at around 700mV forward bias. The whole injection can also be observed for the planar Schottky diode with the barrier height of 805meV at around 750mV, whereby it is less pronounced, as a higher forward voltage would be necessary in order to drive this device into strong forward bias.

The forward characteristics is Figure 11 were all measured at room temperature. At higher temperatures the curves will of course shift but the order and the discussed tendencies will remain intact.

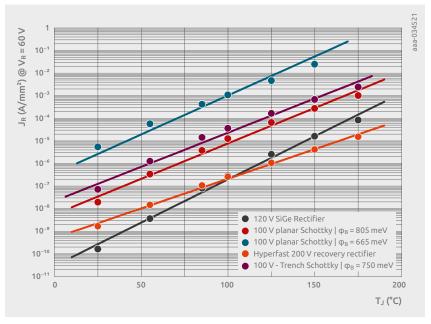

Now let's consider the reverse characteristics of the same devices which were discussed in forward bias. Again, for this comparison of different technologies it is appropriate to normalize their reverse currents with respect to the active area of the die. However, a graphic of the leakage current density at all temperatures and all voltages fr all technologies would quickly become very confusing. For this reason we have concentrated on a fixed voltage and will discuss development of the leakage current density over the temperature range for a fixed voltage. A reverse bias voltage of –60V has been chosen for comparing the reverse characteristics of the different 100V technologies. –60V is high enough to reflect the blocking capability of the diodes but also low enough not to be affected by the incipient breakdown of the device.

The result is displayed in Figure 12. The hyper fast recovery rectifier, a device based on a pn junction, has a very low leakage level. The leakage current density increases approximately one order of magnitude for every 40°C increase in junction temperature. Interestingly, the leakage current density for the SiGe diode is even below the level of the recovery rectifier up to a junction temperature of 90°C. The rate at which the leakage current of the SiGe diode increases is steeper than for the hyper fast recovery rectifier. This is due the hybrid nature of the SiGe diode, also featuring a Schottky contact. Overall, the level of the leakage current density for the SiGe diode is very low, comparable to the hyper fast recovery rectifier. Together with the advantages already discussed over the hyper fast recovery rectifier in the

forward direction (see Figure 11), the value proposition of the SiGe diode becomes apparent. With regard to Schottky diodes, the influence of the electron barrier height as the determining factor can be seen quite clearly. As expected the planar Schottky device with the lowest barrier height (665meV) shows the highest leakage current density, which again illustrates the well-known trade-off between the forward voltage drop and the leakage current for Schottky diodes. The exponential dependence of the leakage current on the barrier height leads to a significantly reduced leakage current levels for the device with the barrier height of 805meV compared to the one with 665meV. In the case of the trench diode, despite the advantages in the forward direction, there are no disadvantages in the reverse bias. The leakage current is determined by the barrier height and the trench technology helps to control the course of the leakage current over the reverse voltage despite the high doping level in the epitaxial drift layer. (This is not shown in this graph, please refer to a Trench Schottky diode data sheet.)

**Figure 12** | Dependence of the leakage current density (normalized leakage current with respect to the active area) at a reverse bias voltage of –60V on the junction temperature for different 100V technologies.

In many applications, a diode is not operated statically, but it is switched on and off continuously. The switching performance of the diode is critical for the efficiency of a system, such as, for example switched-mode converters.

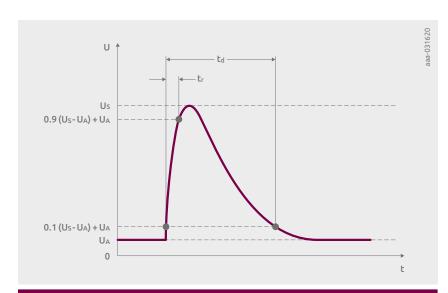

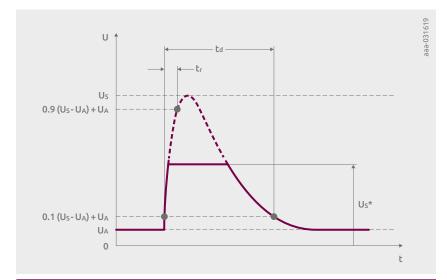

#### 2.4.1 Forward recovery

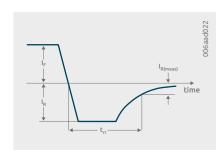

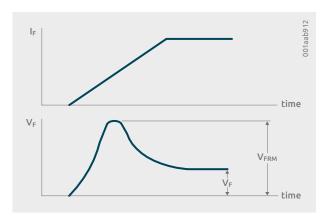

When a diode is switched on, it takes some time for the low-doped drift zone to become flooded with charge carriers. Thus, an increased initial forward voltage drop can be observed when the diode is switched on, because the drift zone does not yet have the necessary conductivity. This so-called forward recovery of the diode is characterized by the parameter  $V_{FRM}$  which describes the switch-on voltage peak and the forward recovery time  $t_{fr}$ . Depending on the thickness and doping of the drift layer, the forward recovery can be quite noticeable and must be considered during circuit design.

Figure 13 | The ramp reverse recovery definition for diodes.

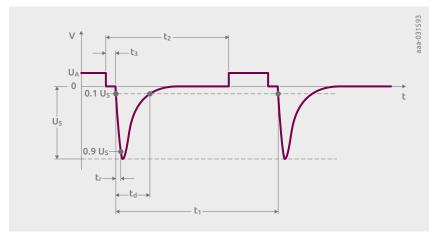

#### 2.4.2 Reverse recovery

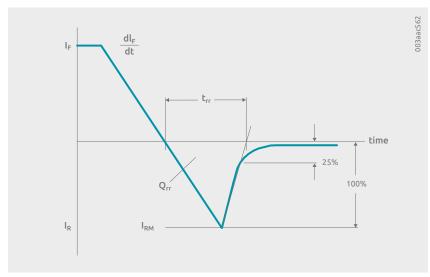

Reverse recovery describes the dynamics with which the diode switches from the forward direction into the reverse blocking stage. When the diode is biased in the forward direction, the bulk material is flooded with charge carriers. If the polarity of the voltage across the diode is now reversed, it takes a finite amount of time until these excess charge carriers are removed. Only then can the space-charge region build up and the reverse voltage can be taken by the diode.

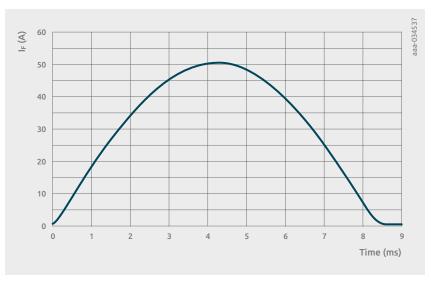

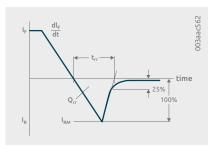

Figure 13 illustrates the defined parameters of the ramp reverse recovery. First, the diode is biased in forward direction, carrying the current I<sub>F</sub>. It is obvious that the level of the forward current has a significant impact on the excess charge in the device and therefore on the dynamics of how fast the stored charge can be removed. This impact will be discussed later in detail. The rate di/dt defines how fast the forward current through the diode is switched off. Here, too, it is evident that a higher di/dt places higher demands on the switching performance of the diode. As shown in Figure 13, the current through the diode even passes the zero line and becomes negative. Notice that at this point that there is still excess charge in the device and no space-charge region has yet built up. The space-charge region starts to build up when the maximum reverse current I<sub>RM</sub> is reached, and then it will take over the reverse voltage. The negative current starts to decrease while the reverse voltage across the diode starts to increase. Eventually the negative current through the device adjusts to the leakage current of the diode. The time between the point when the current crosses the zero line and becomes negative and the point in time when it reaches 25% of the maximum reverse current  $I_{RM}$  (this point being extrapolated linearly as shown is the graph – in some data sheets 10% is specified instead of 25%) is called reverse recovery time  $t_{rr}$ . The next important parameter is the stored charge  $Q_{rr}$  in the device which corresponds to the area below the horizontal zero line (the integral of the diode current within  $t_{rr}$ ).

After defining the parameters of the ramp reverse recovery let's have a look how these parameters impacts the switching losses in a switched-mode converter.

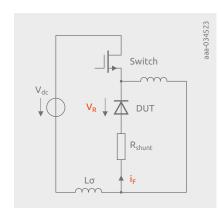

**Figure 14** | Double-pulse test: basic circuit used for characterizing the switching behavior of the diode.

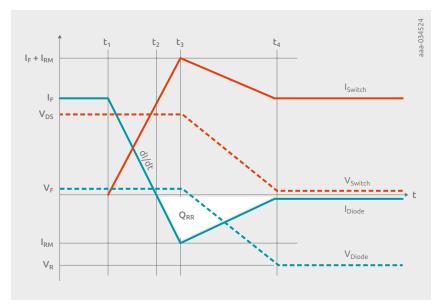

Figure 15 | Graph showing current and voltage waveforms of a diode and the associated switch during the diode turn-off phase.

Figure 14 shows a double pulse testing circuit. Double pulse testing is the standard method for measuring the switching performance of a semiconductor device. It consists basically of a switch which is used to charge the inductance with magnetic energy. By adjusting the width of the first pulse, the required current through the inductance is set while the diode is biased in reverse direction. Then the switch is turned off and the second pulse turns on the device under test (DUT). At this point. the turn-on behavior of the diode can be investigated (forward recovery). Now the current is flowing through the diode. At a given point,  $t_1$  as shown in Figure 15, the switch turns on and starts to turn off the current through the diode with the defined di/dt ramp. As discussed, the diode current will even turn negative and intersects the x-axis at t<sub>2</sub>. At this point the switch is still carrying the entire input voltage. Only at time  $t_3$  is the maximum reverse current reached and the spacecharge region of the diode begins to form. Now the diode starts to take over the voltage. From this point on, power loss needs to be dissipated in the diode. contributing to switching losses of the circuit. As seen at t<sub>3</sub> the switch must not only carry the current  $I_F$ , but also the recovery current  $I_{RM}$  of the diode, which increases the switching losses in the switch further. At t<sub>4</sub> the space-charge region in the diode is fully built up and the reverse voltage across the diode equalizes to the input voltage.

# 2.5 Benchmarking of different technologies in terms of switching

In this section the switching behavior of different diode technologies will be presented and discussed. As an informative introduction, the operating points and evaluation parameters as well as their calculation method are first presented.

#### 2.5.1 Evaluation parameters

Unlike the operating parameters which are manually set beforehand, evaluation parameters are extracted and calculated from the measured current trajectory. They directly represent the switching performance.

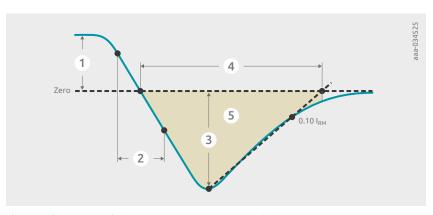

Figure 16 shows an approximated reverse recovery current trajectory. The corresponding explanation of the numbers provides the definitions of the evaluated parameters which were extracted and used for the evaluation of the diode performances (which are number 1 to 5).

Figure 16 | Schematic of the reverse recovery trajectory with the corresponding parameters.

- 1.  $I_F$  Forward conduction current

- 2.  $di_{F}/dt$  Rate of diode current change through zero crossing

- 3. I<sub>RM</sub> Maximum reverse recovery current

- 4.  $t_{rr}$  Reverse recovery time, measured from zero crossing where the diode current changes from positive to negative, to the point at which the straight line through  $I_{RM}$  and 10% of  $I_{RM}$  passes through zero (10% level used for following measurements).

- 5.  $Q_{rr}$  Reverse recovery charge: area under the curve defined by  $I_{RM}$  and  $t_{rr}$

- 6. Softness factor  $SF_{rr}$  Quotient of di/dt before  $I_{RM}$  occurs divided by di/dt after I<sub>RM</sub> occurs

#### Operating points switching performance

The following list gives an overview of the different parameter variations under which the reverse recovery was measured and compared:

Units for all the following tables of the evaluation parameters:

- Q<sub>rr</sub> is given in [nC]

- I<sub>RM</sub> is given in [A]

- t<sub>rr</sub> is given in [ns]

- SF<sub>rr</sub> is dimensionless

| Different parameter variations   |                |                |              |     |  |  |  |  |  |  |  |

|----------------------------------|----------------|----------------|--------------|-----|--|--|--|--|--|--|--|

| Current edge steepness (in A/ns) | -0.4<br>(±20%) | -0.7<br>(±20%) | -1<br>(±20%) |     |  |  |  |  |  |  |  |

| DC link voltage (in V)           | 24             | 48             | 75           | 90  |  |  |  |  |  |  |  |

| Turn-off current (in A)          | 1              | 3              | 5            |     |  |  |  |  |  |  |  |

| Case Temperatures (in °C)        | -40            | 25             | 85           | 150 |  |  |  |  |  |  |  |

Please notice that there is a 'cross-influence' of the listed operating parameters. As an example, the turn-off current proportionally increases the current edge steepness di/dt, without any other changes in the gate circuit. Once the influence of changing the turn-off current or dc-link voltage exceeds a set limit, the gate resistor must be adjusted in order to guarantee as similar slope gradients as possible. Therefore, small variations in the di/dt values can be avoided. For that reason, the edge steepness parameters are given in ranges in which the di/dt values were held for the specific measurements. Nevertheless, comparability in the following measurements is guaranteed within each set of measurements, as the operating conditions were absolute equal and therefore free of di/dt variations or other cross-interferences. Here, a set is defined as the measurement of all diodes at the same operating point.

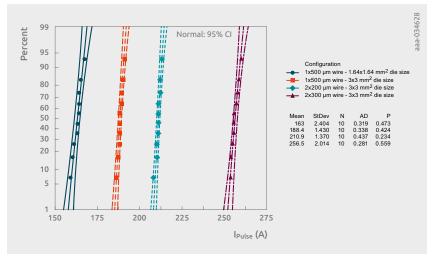

#### 2.5.2 Sample selection

The different diode technologies investigated in this section are: silicon germanium, Trench Schottky, Planar Schottky and reverse recovery diode. Table 1 summarizes the chosen products.

Naturally, the competing devices for analysis were selected to have as similar operating ranges as possible and the same packaging (SOD128). As no 100V recovery rectifiers were available for the chosen current range, 200V types were used instead.

Table 1: Rated current and voltage of the compared devices.

| Product       | Technology          | Voltage/<br>current Rating | Package |

|---------------|---------------------|----------------------------|---------|

| PMEG120G30ELP | Silicon germanium   | 120V/3A                    | SOD128  |

| PNE20030EP    | Hyper fast recovery | 200V/3A                    | SOD128  |

| RB058LAM150TR | Planar Schottky     | 150V/3A                    | SOD128  |

| PMEG100T30ELP | Trench Schottky     | 100V/3A                    | SOD128  |

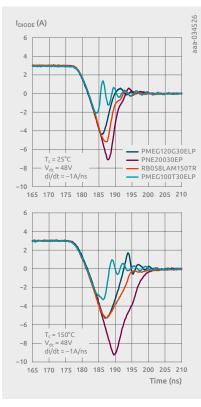

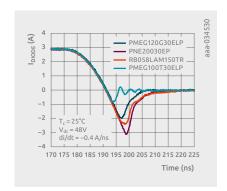

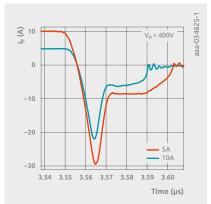

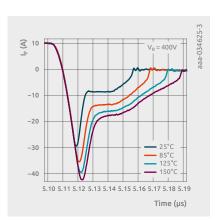

#### 2.5.3 Impact of temperature on the switching performance

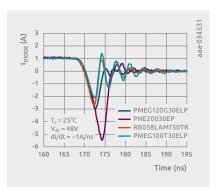

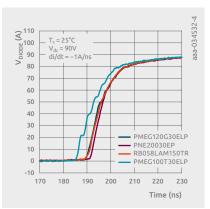

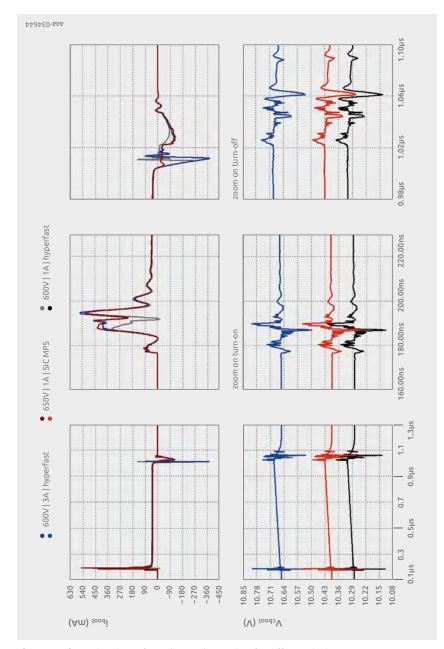

Figure 17 depicts the forward current I<sub>E</sub> during the transition from forward bias into reverse direction for a dc-link voltage of 48V and a turn-off current of 3A. at room temperature and at 150°C case temperature. Only the temperature as an operating parameter was varied as stated below. The key factor in this comparison is the very steep current slope of di/dt = -1A/nswhich is very close to the real application and 5 to 10 times higher compared to usual test conditions in datasheets.

Fixed operating parameter:

$V_{dc} = 48V$

I==3A

$di/dt = -1 (\pm 20\%)$

Varied operating parameter:

Case temperature -

$T_c = [-40^{\circ}C, 25^{\circ}C, 85^{\circ}C, 150^{\circ}C]$

**Figure 17** | Reverse recovery current for different technologies at room temperature and at 150°C case temperature.  $V_{dc} = 48V$ ,  $I_E = 3A$  and di/dt = -1A/ns.

Table 2 lists the corresponding evaluated parameters  $Q_{rr}$ ,  $I_{rrm}$ ,  $t_{rr}$  and SF<sub>rr</sub> which were derived from the figures above.

Units for all the following tables of the evaluation parameters:

- Q<sub>rr</sub> is given in [nC]

- I<sub>RM</sub> is given in [A]

- t<sub>rr</sub> is given in [ns]

- SF<sub>rr</sub> is dimensionless

Table 2: Reverse recovery evaluation parameters for different temperatures. Other operating parameters kept constant at  $V_{dc} = 48V$ ,  $I_F = 3A$  and di/dt = -1A/ns.

| Product       |       | Q <sub>rr</sub> ( | <u>@</u> Т= |       | I <sub>RM</sub> @T= |      |      |       |

|---------------|-------|-------------------|-------------|-------|---------------------|------|------|-------|

|               | -40°C | 25°C              | 85°C        | 150°C | -40°C               | 25°C | 85°C | 150°C |

| PMEG120G30ELP | 13.6  | 19.1              | 25.5        | 33.1  | 4.02                | 4.42 | 4.87 | 5.3   |

| PNE20030EP    | 25.8  | 37.3              | 52.1        | 80.5  | 6.28                | 7.11 | 8.12 | 9.24  |

| RB058LAM150TR | 11.9  | 26.3              | 33.5        | 41.6  | 5.18                | 5.18 | 5.2  | 5.25  |

| PMEG100T30ELP | 4.8   | 4.7               | 6.8         | 14    | 2.3                 | 2.1  | 2.3  | 3.32  |

| Product       |       | t <sub>rr</sub> @ | PT=  |       | SF <sub>rr</sub> @T= |      |      |       |

|---------------|-------|-------------------|------|-------|----------------------|------|------|-------|

|               | -40°C | 25°C              | 85°C | 150°C | -40°C                | 25°C | 85°C | 150°C |

| PMEG120G30ELP | 6.4   | 8.24              | 9.7  | 11.2  | 0.66                 | 0.87 | 0.94 | 0.96  |

| PNE20030EP    | 8.2   | 11.1              | 13.6 | 18    | 0.59                 | 0.82 | 0.94 | 1.17  |

| RB058LAM150TR | 5.3   | 10.6              | 12   | 14.2  | 0.36                 | 1    | 1.19 | 1.37  |

| PMEG100T30ELP | 3.6   | 3.8               | 4.9  | 6.9   | 0.36                 | 0.42 | 0.44 | 0.34  |

#### **Key observations**

For nearly all operating points, the Trench Schottky diode outperforms all other competing diodes. This holds for  $Q_{rr}$ ,  $I_{RM}$  and  $t_{rr}$  values. As a trade-off compared to the other technologies, the Trench Schottky diode shows a higher snappiness and subsequent oscillation. It is also remarkable that the 120V SiGe diode has less stored charge than the 150V planar Schottky diode, in spite of the very low leakage current that this product has. As expected, the hyper fast recovery rectifier switches the slowest and has the highest amount of stored charge. Here the bipolar nature of the hyper fast diode becomes noticeable despite the life-time killing material in the epitaxial layers. However, one should also note the smooth switching of this hyper fast diode.

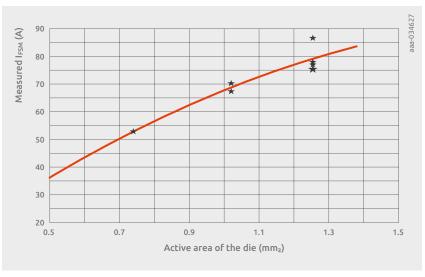

#### 2.5.4 Why is the Trench Schottky diode superior in terms of switching

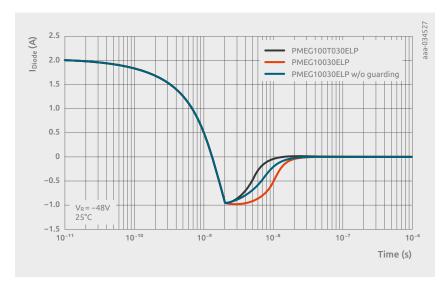

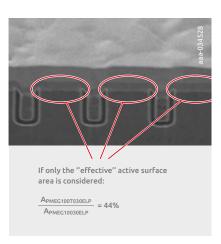

The measurements in Figure 17 illustrate the superior performance of Trench Schottky diodes in terms of switching when compared to all other technologies. A look at the data sheets shows that the Trench Schottky diode even shows the highest parasitic capacitance compared to all the other products. In this respect the question arises how this happens. The answer can be found in Figure 8. As shown in the cross section, there is no guard ring in the termination design for the 100V Trench Schottky diodes. The impact can be best be investigated by using physical device simulations. For this reason, the switching behavior of the planar Schottky diode PMEG10030ELP and of the Trench Schottky diode PMEG100T030ELP was simulated. The simulated switching performance is illustrated in Figure 18. Device simulations confirm the measured superior switching performance of the Trench Schottky diode PMEG100T030ELP compared to its planar counterpart PMEG10030ELP. In the device simulation it is easy to omit the guard ring of the planar Schottky diode and to investigate the impact of the guard ring on the switching performance. The blue curve in Figure 18 shows the planar diode without the guard ring. In fact, the planar Schottky diode without guard ring is now approaching the Trench Schottky diode. However there is still a gap between the planar Schottky diode without guard ring and the Trench Schottky diode in terms of Q<sub>rr</sub> and t<sub>rr</sub>. Obviously, the missing guard ring in the Trench Schottky device can explain a large part of the difference, but not all. The second factor why the Trench-Schottky diode switches much faster and with less stored charge is the significant size difference of the active areas. For a fair comparison of the die sizes, it is necessary to subtract the dead area caused by the trenches from the active area of the Trench Schottky diode, comparing only the effective active area that really contributes to the forward current to that of its planar counterpart. This is shown in Figure 19. This way to compare the active areas reveals that the Trench Schottky PMEG100T030ELP occupies only 44% of the active area of its planar counterpart PMEG10030ELP. In summary, the superior switching behavior of the Trench Schottky diode can be explained by the lack of a guard ring with a parasitic pn junction and by its much smaller active area compared to other devices. Please notice that the impact of the guard ring on the switching behavior is very much die size dependent, as the area of the guard ring with a fixed width increases linearly, while the active area itself increases exponentially with increasing die pitch. So the bigger the die size the less pronounced is the impact of the guard ring on the switching performance. The influence of the guard is also dependent on how far the diode is biased in the forward direction, and thus how much the guard ring is triggered to conduct current. We will see in 2.5.6 that this has a huge impact on the switching performance.

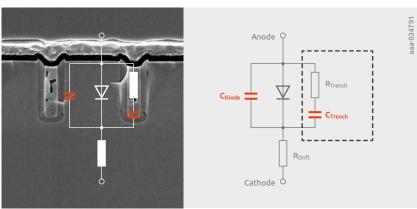

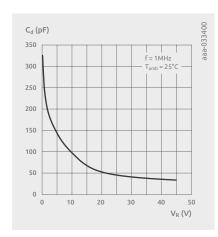

The reason for the switching behavior is now clarified. But the question still remains: why is the parasitic capacitance of Trench Schottky diode so large and why it is not affecting the switching performance? This can again be answered with a look at the cross section of the device. The cross section of a Trench unit cell is shown in Figure 20, together with the resulting equivalent circuit diagram of the cell. In this Figure one can see the parasitic capacitance  $C_{diode}$  that exists in each Schottky diode due to the metal-semiconductor junction in the device. However, with Trench Schottky diodes there is a second parasitic capacitance in the device structure. Called C<sub>Trench</sub>, this capacitance is caused by the thin dielectric in the trenches which are filled with poly silicon. This high parasitic capacitance contributes to the overall parasitic capacitance of the Trench Schottky diode, resulting in a high specified parasitic capacitance in the data sheet. However the parasitic capacitance  $C_{\mathsf{Trench}}$  can be quickly charged and discharged through the highly doped poly silicon layer in the trenches. It is not affected by the dynamics of charge carriers in the drift region, which is the case for the capacitance  $C_{diode}$ .

Figure 18 | Simulated ramp reverse recovery of three different diodes. PMEG100T030ELP (Trench Schottky), PMEG10030ELP (planar Schottky) and PMEG10030ELP without guard ring.

Figure 19 | For a fair comparison of the die sizes, only the effective active areas should be compared. Using this method to compare active areas reveals that the Trench Schottky PMEG100T030ELP occupies only 44% of the active area of its planar counterpart PMEG10030ELP.

Figure 20 | Cross section of a unit cell in a Trench Schottky diode and the resulting equivalent circuit diagram of the Trench Schottky diode. The thin dielectric in the Trenches contributes to a high overall parasitic capacitance of the Trench Schottky diode.

#### 2.5.5 Impact of the slope gradient on switching performance

In this section the reverse recovery process is evaluated for different values of the slope steepness di/dt. Figure 21 shows the decrease to di/dt = -0.4A/ns as a reference. The quantified parameter including the ones for di/dt = -0.7A/ns are listed in Table 3.

Fixed operating parameter:

$V_{dc} = 48V$

$I_F = 3A$

$T_c = 25^{\circ}C$

Varied operating parameter:

Slope steepness:

di/dt = -0.4A/ns

di/dt = -0.7A/ns

Figure 21 | Reverse recovery current for lower current slope steepness of -0.4A/ns. Other operating parameters kept constant at  $V_{dc}$  = 48V,  $I_F$  = 3A and  $T_c$  = 25°C.

nexperia | Design Engineer's Guide

Table 3: Reverse recovery evaluation parameters for slope steepness.

| Other operating parameters kept constant at $V_{dc}$ = 48V, $i_F$ = 3A and $T_c$ = 25°C. |       |      |                   |      |                   |      |                   |      |                    |  |  |  |

|------------------------------------------------------------------------------------------|-------|------|-------------------|------|-------------------|------|-------------------|------|--------------------|--|--|--|

| Product                                                                                  |       | Qn   | Q <sub>rr</sub> @ |      | I <sub>RM</sub> @ |      | t <sub>rr</sub> @ |      | SF <sub>rr</sub> @ |  |  |  |

|                                                                                          | A/ns  | -0.4 | -0.7              | -0.4 | -0.7              | -0.4 | -0.7              | -0.4 | -0.7               |  |  |  |

| PMEG120G3                                                                                | 30ELP | 12.6 | 15.4              | 2    | 2.8               | 13.4 | 11.4              | 1.5  | 1.3                |  |  |  |

| PNE20030E                                                                                | Р     | 22.7 | 28.3              | 3.1  | 4.4               | 16.8 | 14.6              | 1.2  | 1.1                |  |  |  |

| RB058LAM150TR                                                                            |       | 20   | 22.7              | 2.4  | 3.3               | 18.7 | 14.6              | 1.7  | 1.4                |  |  |  |

| PMEG100T3                                                                                | 0ELP  | 2.5  | 3.3               | 0.8  | 1.3               | 5    | 4.4               | 0.78 | 0.5                |  |  |  |

#### **Key observations**

The Trench Schottky diode also remains superior to all competing technologies at lower switching speeds. Nothing else changes in the order in terms of switching speed and amount of stored charge, with SiGe in second place and planar Schottky and hyperfast diode in third and fourth place.

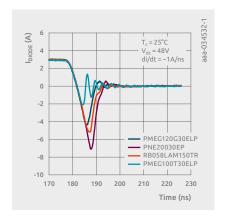

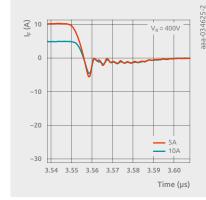

#### 2.5.6 Impact of the turn-off current on switching performance

The diodes were also tested for different turn-off currents. The turn-off current has a significant influence on the di/dt and therefore on the reverse recovery process. Figure 22 illustrates the reduced turn-off current of 1A. The evaluated parameter for a higher turn-off current of 5A where no ranking changes occur, is listed in Table 15.

Fixed operating parameter:

$V_{dc} = 48V$

$T_c = 25^{\circ}C$

$di/dt = -1 (\pm 20\%)$

Varied operating parameter:

Turn-off current:

$I_{F} = [1A; 5A]$

Figure 22 | Reverse recovery current for 1A turn-off current. Other operating parameters kept constant at  $V_{dc}$  = 48V,  $T_c$  = 25°C and di/dt = -1A/ns.

Table 4: Reverse recovery evaluation parameters for different turn-off current.

| Other operating parameters kept constant at $V_{dc}$ = 48V, $T_c$ = 25°C and di/dt = - 1A/ns. |                  |                   |      |                   |     |                   |      |                    |      |  |  |  |  |

|-----------------------------------------------------------------------------------------------|------------------|-------------------|------|-------------------|-----|-------------------|------|--------------------|------|--|--|--|--|

| Product                                                                                       |                  | Q <sub>rr</sub> @ |      | I <sub>RM</sub> @ |     | t <sub>rr</sub> @ |      | SF <sub>rr</sub> @ |      |  |  |  |  |

| Product                                                                                       | i <sub>F</sub> = | 1A                | 5A   | 1A                | 5A  | 1A                | 5A   | 1A                 | 5A   |  |  |  |  |

| PMEG120G3                                                                                     | 0ELP             | 7.5               | 31   | 3                 | 6.1 | 4.7               | 9.4  | 0.73               | 0.74 |  |  |  |  |

| PNE20030E                                                                                     | P                | 17.6              | 50.6 | 5.5               | 8.6 | 6.4               | 12   | 0.5                | 0.77 |  |  |  |  |

| RB058LAM1                                                                                     | 50TR             | 5.5               | 49   | 2.7               | 7.4 | 3.8               | 12.3 | 0.4                | 0.88 |  |  |  |  |

| PMEG100T3                                                                                     | 0ELP             | 4.3               | 6    | 2.1               | 2.6 | 3.4               | 4    | 0.36               | 0.4  |  |  |  |  |

#### **Kev observations**

The investigated products have a nominal current rating of 3A. The higher turn-off current results in a higher forward voltage drop, triggering the parasitic pn junction in the termination area even more. Therefore, as shown in Table 4 there is a significant increase at 5A turn-off current for all diode technologies that use the guard-ring as termination concept in terms of  $Q_{rr}$ ,  $I_{rrm}$  and  $t_{rr}$  values. The impact on Trench Schottky diodes is much less pronounced due to the lack of pn junction in the device structure. At the same time, it is also very important to note that at

lower turn-off current of 1A (well below the current rating of the products) the advantage of the Trench-Schottky diode diminishes, as the parasitic pn diode loses importance in the structure of the other diodes. As shown in Table 4 for 1A turn-off current, the planar Schottky product is almost on par with the Trench Schottky in terms of  $Q_{rr}$ ,  $I_{rrm}$  and  $t_{rr}$ . This is consistent with the simulation results discussed in 2.5.4. Consequently, depending on the current level and the current density of the device, in addition to the switching frequency, duty cycle and temperature, the optimal diode technology for each application may be a different one.

In summary, next to ambient temperature, the turn-off current has the greatest influence on switching behavior of the diodes and should be taken into account during circuit design.

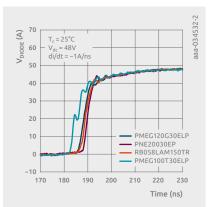

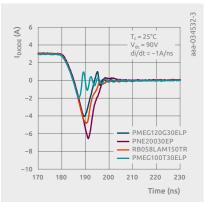

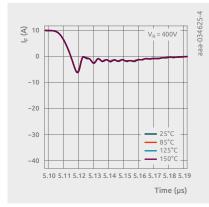

#### 2.5.7 Impact of the reverse voltage on switching performance

In this section, the variation of the dc-link voltage is investigated and presented. The reverse voltage during the switching process is depicted on the right side in Figure 23 next to the corresponding current trajectory. Quantified results are presented in Table 5.

Fixed operating parameter:

$I_F = 3A$

$T_c = 25^{\circ}C$  $di/dt = -1A/ns (\pm 20\%)$

Varied operating parameter:

dc link voltage:

$V_{dc} = [48V; 90V]$

Table 5: Reverse recovery evaluation parameters for different dc-link voltages V<sub>dc</sub>

| Diode         |                   | Q <sub>rr</sub> @ |      | I <sub>RN</sub> | 1@  | t <sub>rr</sub> @ |      | SF <sub>rr</sub> @ |      |

|---------------|-------------------|-------------------|------|-----------------|-----|-------------------|------|--------------------|------|

| Diode         | V <sub>dc</sub> = | 75V               | 90V  | 75V             | 90V | 75V               | 90V  | 75V                | 90V  |

| PMEG120G30ELP |                   | 19.3              | 19.3 | 4.1             | 4.1 | 8.6               | 8.9  | 0.93               | 0.74 |

| PNE20030EP    |                   | 38.1              | 37.9 | 6.8             | 6.6 | 12                | 12.3 | 0.93               | 0.96 |

| RB058LAM150TR |                   | 27.3              | 27.4 | 5               | 4.8 | 11.1              | 11.3 | 1.1                | 1.1  |

| PMEG100T30ELP |                   | 4.5               | 4.5  | 2               | 1.9 | 3.8               | 3.8  | 0.42               | 0.45 |

Figure 23 | Reverse recovery and reverse voltage for different dc-link voltages. Fixed operating parameters  $I_F = 3A$ ,  $T_c = 25$ °C, di/dt = -1A/ns

#### **Key observations**

The trajectories of the voltages are consistent with the corresponding current curves, both in terms of oscillation and slope steepness. The performance ranking among the diodes remains unchanged from the first observations with the Trench Schottky diodes being dominant in terms of  $Q_{rr}$ ,  $I_{rrm}$  and  $t_{rr}$ . The 120V SiGe product takes second place and remains ahead of the Planar Schottky and the hyper fast recovery diodes.

#### 2.6.1 Introduction

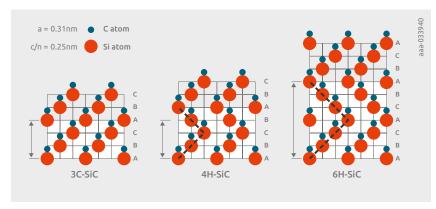

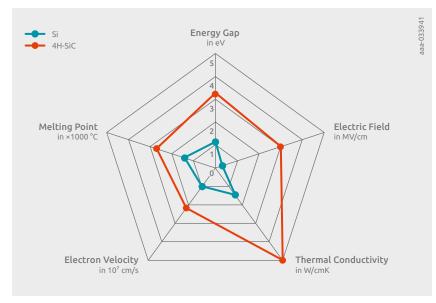

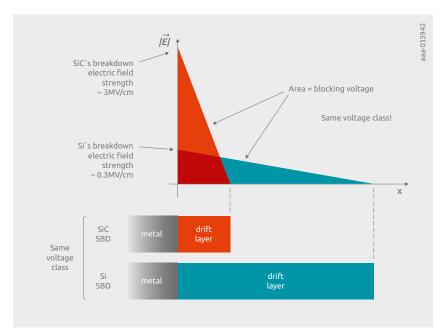

Silicon carbide, often simply abbreviated as SiC, is a compound semiconductor that consists of both silicon and carbon atoms. Unlike other materials, silicon carbide exists in many crystal structures. This phenomenon is called polymorphism. For SiC, more than 250 different polytypes are known. Each polytype has its own unique properties. For commercial power electronic power devices, the polytype 4H-SiC is predominantly used. The arrangement of a 4H-SiC crystal is depicted in Figure 24.

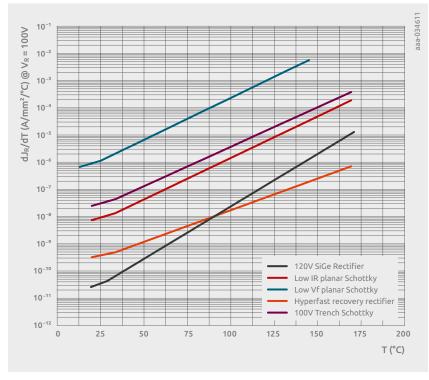

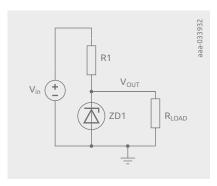

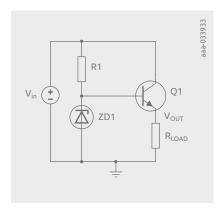

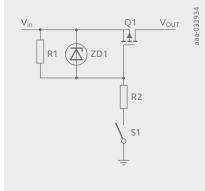

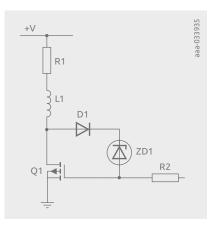

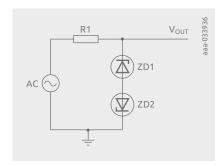

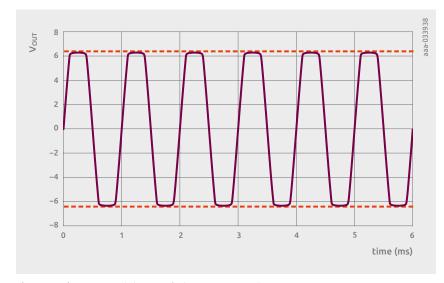

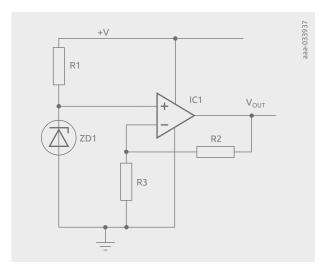

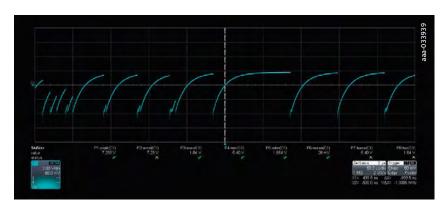

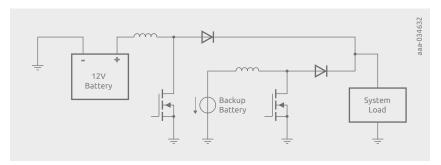

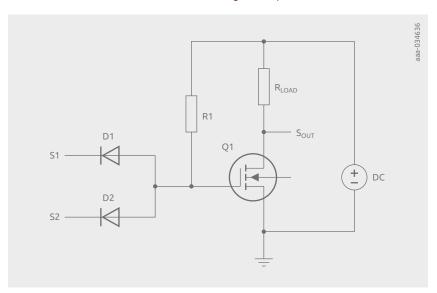

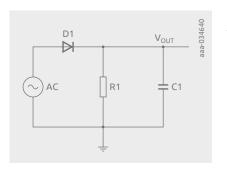

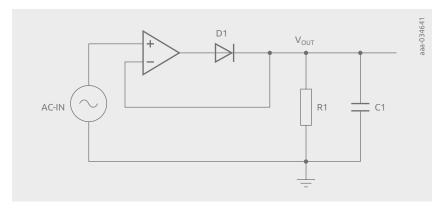

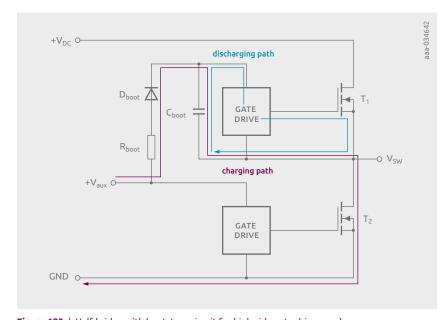

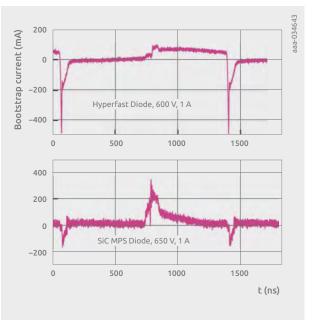

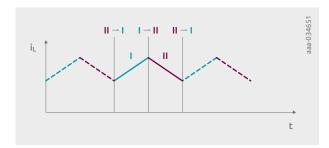

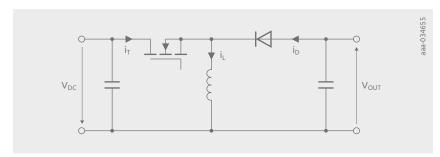

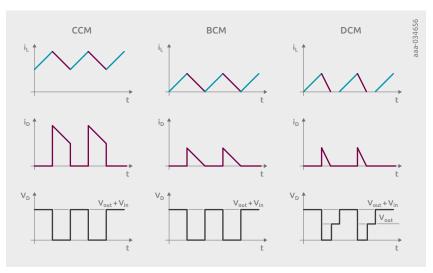

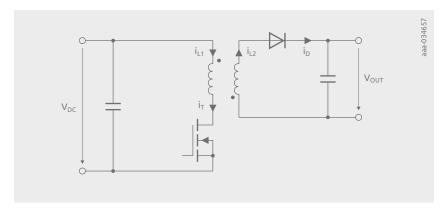

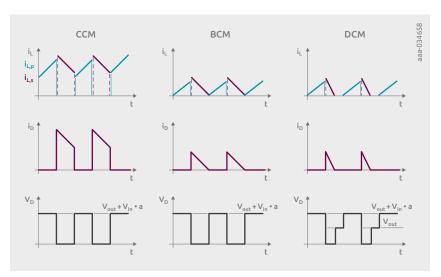

Figure 24 | SiC polytypes